清华用忆阻器制人工神经网络芯片,能效比GPU高两个数量级

2020-02-26 09:47:18爱云资讯1276

传统的计算机将数据储存在内存中,然后传送到处理器运算。这种来回“搬运”数据的活动耗费能源和时间,被认为是冯 诺依曼计算架构的核心瓶颈。

而人类的大脑却并非如此,而是直接在记忆体里计算。被认为具有“存算一体”潜力的忆阻器,因而成为类脑计算领域的热门器件。

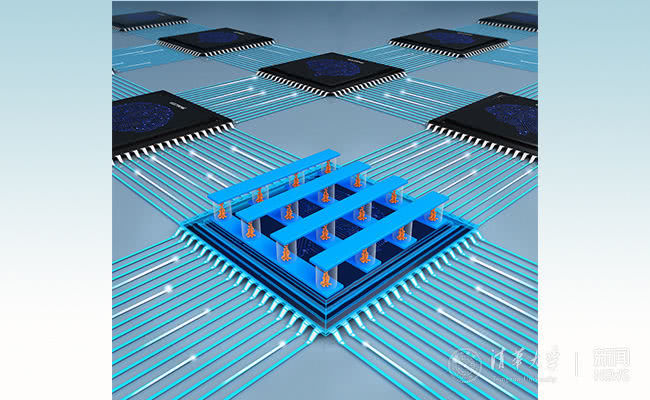

近日,清华大学微电子所、未来芯片技术高精尖创新中心钱鹤、吴华强团队与合作者在顶尖学术期刊、英国《自然》杂志(Nature)在线发表论文,报道了基于忆阻器阵列芯片卷积网络的完整硬件实现。

该存算一体系统在处理卷积神经网络(CNN)时能效比前沿的图形处理器芯片(GPU)高两个数量级,可以说在一定程度上突破了“冯诺依曼瓶颈”的限制:大幅提升算力的同时,实现了更小的功耗和更低的硬件成本。

基于忆阻器芯片的存算一体系统 来源:清华大学

基于忆阻器芯片的存算一体系统 来源:清华大学

什么是忆阻器?

忆阻器,全称记忆电阻器(Memristor),是继电阻、电容、电感之后的第四种电路基本元件,表示磁通与电荷之间的关系,最早由加州大学伯克利分校教授蔡少棠在1971年预言存在,惠普公司在2008年研制成功。

简单来说,这种组件的的电阻会随着通过的电流量而改变,而且就算电流停止了,它的电阻仍然会停留在之前的值,直到接受到反向的电流它才会被推回去,等于说能“记住”之前的电流量。

这种奇妙的效果,其实和神经元突触有相仿之处。再加上忆阻器还具有尺寸小、操作功耗低、可大规模集成(三维集成)等优点,难怪计算机科学家们在忆阻器身上看到了存算一体、低能耗类脑计算的前景。

人工神经网络近年来大放异彩,如果用忆阻器连接成阵列,作为人工神经网络的硬件,会有什么效果?

忆阻器阵列

尽管国内外许多企业、研究机构给予关注,但据清华大学新闻页面报道,当前国际上的忆阻器研究还停留在简单网络结构的验证,或者基于少量器件数据进行的仿真。基于忆阻器阵列的完整硬件实现仍然有很多挑战。

比如,器件方面,需要制备高一致、可靠的阵列;系统方面,忆阻器因工作原理而存在固有缺陷(如器件间波动,器件电导卡滞,电导状态漂移等),会导致计算准确率降低;架构方面,忆阻器阵列实现卷积功能需要以串行滑动的方式连续采样、计算多个输入块,无法匹配全连接结构的计算效率。

通过近年来积累的一些成果,钱鹤、吴华强团队逐渐优化材料和器件结构,制备出了高性能的忆阻器阵列。

2017年5月,该课题组就曾在《自然通讯》报告称,首次实现了基于1024个氧化物忆阻器阵列的类脑计算,将氧化物忆阻器的集成规模提高了一个数量级。这使芯片更加高效地完成人脸识别计算任务,将能耗降低到原来的千分之一以下。

忆阻器神经网络

这次,钱、吴团队集成了8个包括2048个忆阻器的阵列,以提高并行计算的效率。

在此基础上,他们构建了一个五层的卷积神经网络进行图像识别,获得了96%以上的高精度,结果显示,基于忆阻器的卷积神经网络比目前最先进的GPU的能效要高出两个数量级。

这样的提升是如何实现的?原来,为解决器件固有缺陷造成的系统识别准确率下降问题,他们提出了一种新型的混合训练算法,仅需用较少的图像样本训练神经网络,并微调了最后一层网络的部分权重。

与此同时,他们提出了空间并行的机制,将相同卷积核编程到多组忆阻器阵列中,各组忆阻器阵列可并行处理不同的卷积输入块,提高并行度来加速卷积计算。

多个忆阻器阵列并行处理

随着摩尔定律放缓,计算界翘首以待新的架构突破冯诺依曼瓶颈,适应越来越复杂的AI问题。基于忆阻器的存算一体系统在这场角逐中稳步前进。

相关文章

- 源于清华的开源时序数据库IoTDB刷新世界纪录

- 宏碁助力英特尔与清华大学AIGC联合实验中心落成!

- 清华大学经管学院朱武祥教授:五步构建高效的数据飞轮,提升企业核心竞争力

- 郭彦东博士受邀出席清华大学金融PLUS系列产业峰会

- 清华博导郑毓煌力作《解码自控力》重磅上市!

- WAIC特别专访|清华大学梁正:在垂类领域打造具有全球竞争力的“小精尖”行业大模型

- 文心一言数学和中文理解能力全球第?清华最新报告出炉

- 宝德携手清华大学,以高性能计算共筑网络管理与安全新高地

- 第十三届清华脑起搏器论坛在京圆满落幕,共筑患者健康未来

- 签约揭牌!清华合肥院与施罗德集团共建联合研究院

- 亚信科技、清华大学“算力内生网络技术”荣获中国自动化学会“2023科技进步一等奖”

- 长飞公司与清华电子院签订战略合作协议

- 中国信通院联合阿里云、清华大学网络科学与网络空间研究院发布《“DNS+”发展白皮书》

- 京东AIGC大赛走进中国传媒大学和清华美院 高校路演圆满收官

- 腾讯刘杉对话清华陶晓明,探索语义通信与视频编解码跨领域合作新方案

- 海纳千律荣获清华三创大赛全球十强